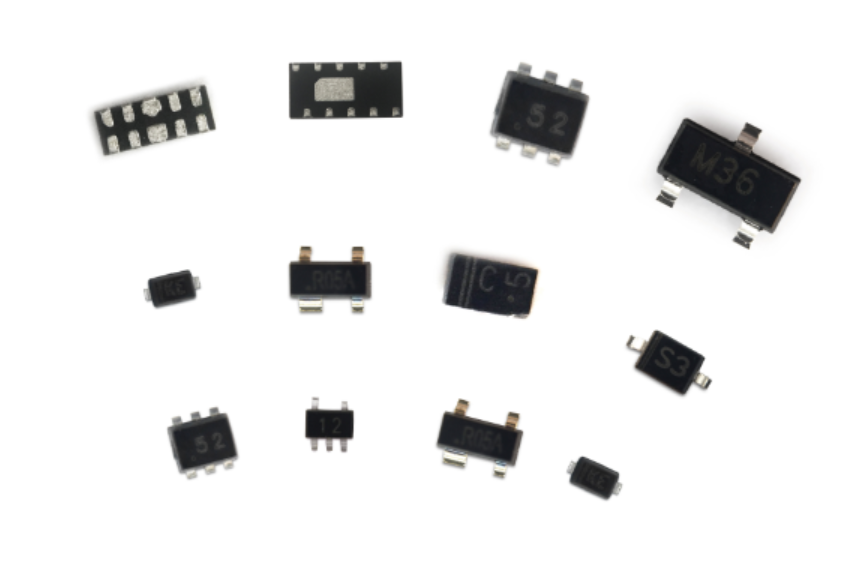

JEDEC最高要求30 KV是因為(wei) 這是一個(ge) 常見的靜電放電(ESD)電壓限製。

ESD是在兩(liang) 個(ge) 物體(ti) 之間發生的靜電放電,可能會(hui) 損壞電子設備或導致數據丟(diu) 失。因此,為(wei) 了確保設備的可靠性和穩定性,JEDEC製定了30 KV的靜電放電標準。這個(ge) 標準是基於(yu) 實際測試和經驗得出的,可以保證設備在正常操作和使用過程中不受到不可接受的靜電放電影響。

JE針對電子芯片靜電放電(ESD)製定了幾個(ge) 標準,主要有以下幾個(ge) 標準號:1. JEDEC JESD22-A114:這個(ge) 標準規定了集成電路(IC)和元件對人體(ti) 模型(HBM)ESD的測試方法和要求。

2. JEDEC JESD22-A115:這個(ge) 標準規定了IC和元件對擴散模型(CDM)ESD的測試方法和要求。

3. JEDEC JESD22-C101:這個(ge) 標準規定了IC和元件對係統級模型(MM) ESD的測試方法和要求。

這些標準定義(yi) 了ESD測試的條件、儀(yi) 器設備和測試流程,以確保芯片能夠在ESD事件下安全運行。每個(ge) 標準針對不同的ESD電壓模型,分別規定了不同的測試方法和測試參數。

熱門新聞

熱門新聞